导读 IT之家 3 月 21 日消息,据三星半导体微信公众号发布的中国闪存市场峰会 2024 简报,其正研发 CMM-H 混合存储 CXL 模组。该模组...

IT之家 3 月 21 日消息,据三星半导体微信公众号发布的中国闪存市场峰会 2024 简报,其正研发 CMM-H 混合存储 CXL 模组。该模组同时包含 DRAM 内存和 NAND 闪存。

IT之家注:作为一种新型高速互联技术,CXL 可提供更高的数据吞吐量和更低的传输延迟,可在 CPU 和外部设备间建立高效连接。

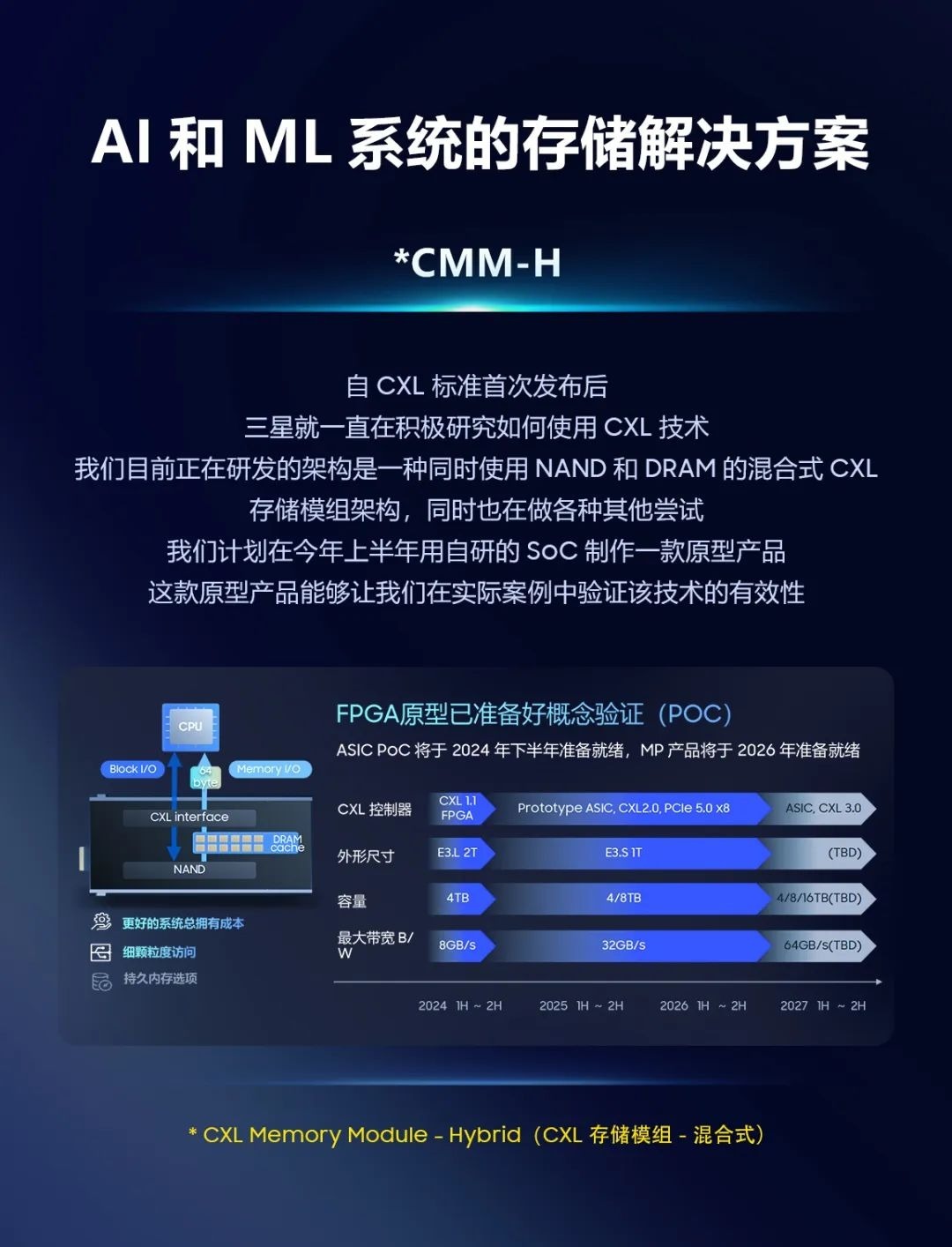

根据三星给出的图示,这一模组可经由 CXL 界面直接在闪存部分和 CPU 之间传输块 I / O,也可经由 DRAM 缓存和 CXL 界面实现 字节的内存 I / O 传输。

CMM-H 模组可实现细粒度访问,降低 TCO,同时也是可能的持久内存选项。

根据三星展示的路线图,其计划在今年上半年制作一款原型 CMM-H 产品。该原型将配备基于 FPGA 的 CXL 1.1 控制器,采用 E3.L 2T 规格,最大容量 4TB,最大带宽 8GB/s。

展望未来商用量产 CMM-H 模组,其基于 ASIC 的成熟控制器将支持 CXL 3.0 规范,容量最大可选 16TB,最大带宽提升至 GB/s,将于 2026 年准备就绪。

此外,在更传统的 CXL-D 纯内存 CXL 存储模组方面,三星计划明年一季度出样 128GB 容量的第二代产品,其采用 1b nm 制程 DRAM 颗粒,速度达 00MT/s。

明年三星还将丰富第二代 CXL-D 模组产品线,512GB 和 256GB 容量产品随后跟上。

免责声明:本文由用户上传,如有侵权请联系删除!