导读东京工业大学的科学家开发出一种先进的锁相环[1](PLL)频率合成器,可以大幅降低功耗。这种数字PLL可以成为蓝牙低功耗(BLE)和其他无线技术的

东京工业大学的科学家开发出一种先进的锁相环[1](PLL)频率合成器,可以大幅降低功耗。这种数字PLL可以成为蓝牙低功耗(BLE)和其他无线技术的有吸引力的构建模块,以支持广泛的物联网(IoT)应用。

作为无线通信系统的关键构建模块,频率合成器需要满足苛刻的要求。虽然模拟PLL频率合成器已成为多年的标准,但物联网行业的工程师越来越多地将注意力转向所谓的数字PLL(DPLL)以实现超低功耗操作。

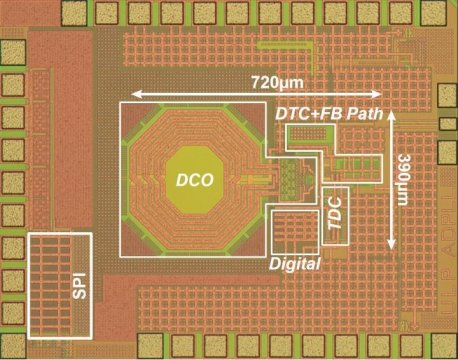

东京工业大学电气与电子工程系副教授Kenichi Okada现在报告了一个分数N DPLL [2],其功耗仅为265微瓦(μW),这个数字不到一半迄今为止实现的最低功耗(980μW)。

研究人员发现,使用自动反馈控制系统可以大大降低整体功耗。“这种自动切换反馈路径的功耗为68μW,整个DPLL的功耗为265μW,”Okada说。

有希望的DPLL可以继续用作处理器,存储器和大量新的物联网设备的组件,通过超低功耗运行,这些设备预计既经济又环保。Okada指出,早期的实验表明,DPLL可以将电池寿命延长四倍。

本文部分基于新能源和工业技术开发组织(NEDO)委托的项目取得的成果。

这项工作将在2019年国际固态电路会议(ISSCC)的频率合成器会议上进行介绍,该会议是世界领先的固态电路和片上系统年度论坛。

技术用词

[1]锁相环(PLL):一种控制系统,用作许多无线电,无线和电信技术的基本组成部分。本研究利用PLL在输入频率的倍数处产生稳定频率的能力。

[2] Fractional-N DPLL:一类新兴的数字PLL,它们可以帮助改善相位噪声。

免责声明:本文由用户上传,如有侵权请联系删除!